计组相关笔记②

W5-W6 指令

VSC 微指令

| Binary | Instruction | Meaning | RTL |

|---|---|---|---|

| 0000 | Jns X | store the PC at address X and jump to X + 1 | MBR ← PC MAR ← X M[MAR] ← MBR MBR ← X AC ← 1 AC ← AC + MBR PC ← AC |

| 0001 | Load X | Load contents of address X into AC. | MAR ← X MBR ← M[MAR] AC ← MBR |

| 0010 | Store X | Store the contents of AC at address X. | MAR ← X MBR ← AC M[MAR] ← MBR |

| 0011 | Add X | Add the contents of address X to AC. | MAR ← X MBR ← M[MAR] AC ← AC + MBR |

| 0100 | Subt X | Subtract the contents of address X from AC. | MAR ← X MBR ← M[MAR] AC ← AC - MBR |

| 0101 | Input | Input a value from the keyboard into AC. | AC ← InREG |

| 0110 | Output | Output the value in AC to the display. | OutREG ← AC |

| 0111 | Halt | Terminate program. | |

| 1000 | Skipcond | Skip next instruction on condition. | If IR[11-10] = 00 then If AC < 0 then PC ← PC + 1 Else If IR[11-10] = 01 then If AC = 0 then PC ← PC + 1 Else If IR[11-10] = 10 then If AC > 0 then PC ← PC + 1 |

| 1001 | Jump X | Load the value of X into PC. | PC ← IR[11-0] |

| 1010 | Clear | set AC to 0 | AC ← 0 |

| 1011 | AddI X | Add Immediate with address X | MAR ← X MBR ← M[MAR] MAR ← MBR MBR ← M[MAR] AC ← AC + MBR |

| 1100 | JumpI X | Use the value at X as the actual address of the location to jump to | MAR ← X MBR ← M[MAR] PC ← MBR |

| Hex Address | Instruction | Binary Contents of Memory Address | Hex Contents of Memory |

|---|---|---|---|

| 100 | Load 104 | 0001000100000100 | 1104 |

| 101 | Add 105 | 0011000100000101 | 3105 |

| 102 | Store 106 | 0010000100000110 | 2106 |

| 103 | Halt | 0111000000000000 | 7000 |

| 104 | 0023 | 0000000000100011 | 0023 |

| 105 | FFE9 | 1111111111101001 | FFE9 |

| 106 | 0000 | 0000000000000000 | 0000 |

LOAD 104

| Step | RTN | PC | IR | MAR | MBR | AC |

|---|---|---|---|---|---|---|

| LOAD 104 | 100 | ---- | — | ---- | ---- | |

| Fetch | MAR ← PC | 100 | ---- | 100 | ---- | ---- |

| IR ← M[MAR] | 100 | 1104 | 100 | ---- | ---- | |

| PC ← PC + 1 | 101 | 1104 | 100 | ---- | ---- | |

| Decode | MAR ← IR[11-0] | 101 | 1104 | 104 | ---- | ---- |

| (Decode IR[15-12]) | 101 | 1104 | 104 | ---- | ---- | |

| Get operand | MBR ← M[MAR] | 101 | 1104 | 104 | 0023 | ---- |

| Execute | AC ← MBR | 101 | 1104 | 104 | 0023 | 0023 |

ADD 105

| Step | RTN | PC | IR | MAR | MBR | AC |

|---|---|---|---|---|---|---|

| ADD 105 | 101 | 1104 | 104 | 0023 | 0023 | |

| Fetch | MAR ← PC | 101 | 1104 | 101 | 0023 | 0023 |

| IR ← M[MAR] | 101 | 3105 | 101 | 0023 | 0023 | |

| PC ← PC + 1 | 102 | 3105 | 101 | 0023 | 0023 | |

| Decode | MAR ← IR[11–0] | 102 | 3105 | 105 | 0023 | 0023 |

| (Decode IR[15–12]) | 102 | 3105 | 105 | 0023 | 0023 | |

| Get operand | MBR ← M[MAR] | 102 | 3105 | 105 | FFE9 | 0023 |

| Execute | AC ← AC + MBR | 102 | 3105 | 105 | FFE9 | 000C |

Store 106

| Step | RTN | PC | IR | MAR | MBR | AC |

|---|---|---|---|---|---|---|

| Store 106 | 102 | 3105 | 105 | FFE9 | 000C | |

| Fetch | MAR ← PC | 102 | 3105 | 102 | FFE9 | 000C |

| IR ← M[MAR] | 102 | 2106 | 102 | FFE9 | 000C | |

| PC ← PC + 1 | 103 | 2106 | 102 | FFE9 | 000C | |

| Decode | MAR ← IR[11–0] | 103 | 2106 | 106 | FFE9 | 000C |

| (Decode IR[15–12]) | 103 | 2106 | 106 | FFE9 | 000C | |

| Get operand | (not necessary) | 103 | 2106 | 106 | FFE9 | 000C |

| Execute | MBR ← AC | 103 | 2106 | 106 | 000C | 000C |

| M[MAR] ← MBR | 103 | 2106 | 106 | 000C | 000C |

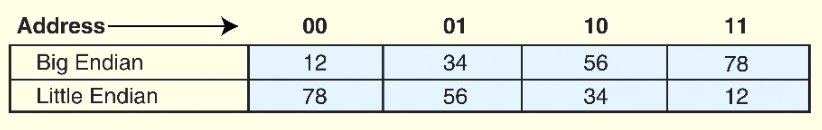

字节序

小端序(Little Endian):小端序是指数据的低位字节存放在低地址端,高位字节存放在高地址端。

大端序(Big Endian):大端序是指数据的高位字节存放在低地址端,低位字节存放在高地址端。

后缀表示法

postfix notation

Z = (X × Y) + (W × U)

这个是?编译原理的?

Z = X Y × W U × +

one-address ISA like VSC infix expression:

PUSH X |

two-address ISA the infix expression:

LOAD R1,X |

three-address ISA

MULT R1,X,Y |

本博客所有文章除特别声明外,均采用 CC BY-NC-SA 4.0 许可协议。转载请注明来自 Xiaotan's Blog!

评论